|

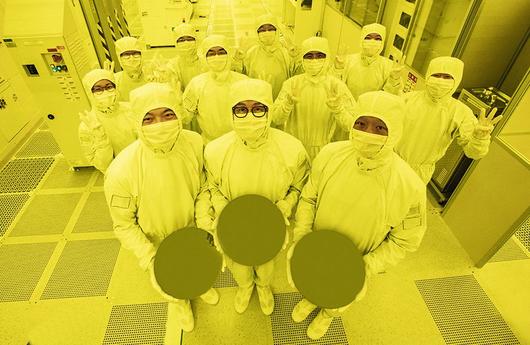

삼성전자가 지난해 6월 세계 최초로 GAA(Gate-All-Around) 기술을 적용한 3나노 파운드리 공정 기반의 초도 양산을 시작하면서 기념 촬영을 하고 있다./삼성전자 제공 |

<이미지를 클릭하시면 크게 보실 수 있습니다> |

삼성전자가 지난해 6월 파운드리(반도체 위탁생산) 1위 대만 TSMC를 제치고 세계 최초로 3㎚(나노미터·1㎚는 10억분의 1m) 파운드리 양산에 성공한 데 이어 2㎚ 시장을 선점하기 위한 업계 경쟁이 치열해지고 있다. 2㎚ 공정 기술 개발에 삼성전자와 TSMC뿐 아니라 미국 인텔과 일본 라피더스도 팔을 걷어붙이고 나섰다. 전 세계 반도체 패권 전쟁이 최첨단 기술력을 요구하는 파운드리 선단 공정 경쟁으로 이어지고 있다는 해석이 나온다.

29일 반도체 업계에 따르면 TSMC는 그래픽처리장치(GPU) 1위 엔비디아와 손잡고 첨단 반도체 기술 협력을 강화한다. 이들은 극자외선(EUV) 노광기를 전 세계 독점 공급하는 네덜란드 반도체 장비업체 ASML를 비롯해 전자설계자동화(EDA) 선두업체인 시놉시스와 협업해 반도체 노광 공정에 가속 컴퓨팅 기술을 도입하기로 했다. 젠슨 황 엔비디아 CEO는 “(나노 패턴을 만드는) 리소그래피가 물리학의 한계에 도달한 현재, 엔비디아와 TSMC, ASML, 시놉시스의 협력으로 2㎚와 그 이후의 기술 개발 기반을 마련했다”고 말했다.

TSMC는 삼성전자보다 6개월가량 늦은 지난해 12월 3㎚ 양산을 시작한 뒤 차세대 제품 개발에 속도를 내고 있다. 니혼게이자이신문은 지난 27일 TSMC가 대만의 실리콘밸리라고 불리는 신주에 최소 80조원을 들여 2㎚ 공정 팹(공장) 4개를 신설하고 있다고 전했다. TSMC는 이곳에서 2025년부터 2㎚ 반도체를 양산한다는 계획을 내놨다.

반도체 산업 재건에 나선 일본에서는 이른바 드림팀이라고 불리는 라피더스가 최첨단 반도체만 단기간에 생산하는 전략을 추구하면서 TSMC·삼성전자에 도전장을 던졌다. 라피더스는 일본 정부가 700억엔(약 6650억원)을 지원하고 소니, 도요타, 키옥시아 등 일본 대표 기업 8곳이 투자해 세운 첨단 반도체 회사다. 이들은 향후 5년간 슈퍼컴퓨터와 인공지능(AI), 자율주행차 등에 쓰일 첨단 반도체 연구 개발에 몰두하고, 2027년 2㎚ 이하 제품을 양산한다는 목표를 내걸었다.

라피더스는 TSMC·삼성전자와 같은 대형 업체와의 경쟁에서 살아남는 비책으로 양적 경쟁이 아닌 다품종 소량 생산 모델을 제시했다. 니혼게이자이는 “일본 업체들은 구매력이 낮아 첨단 반도체를 확보하는 데 실패하는 경향이 있다”며 “2㎚로 가면 이런 상황은 더 악화할 수 있어 도요타 등 일본 기업들이 자기 주문을 소량이라도 받아줄 수 있는 라피더스에 기꺼이 투자하는 것”이라고 설명했다.

인텔은 2021년 파운드리 시장에 재진출한 뒤 정부 지원을 등에 업고 투자를 늘리는 중이다. 최근 2년 사이 미국 내 파운드리 공장 4개의 건설 계획을 내놨고, 내년 3㎚ 양산에 이어 2024년 내 2㎚ 반도체를 양산하겠다는 목표를 세웠다. 이달 초에는 2㎚와 1.8㎚ 기술을 개발했다고 발표했다. 업계 관계자는 “인텔은 아직 시장에서 10㎚ 이하로 증명된 솔루션이 없다”며 “2㎚ 이하에 앞서 10㎚ 이하 공정을 잘 할 수 있는지부터가 관건이다”라고 말했다.

|

그래픽=손민균 |

<이미지를 클릭하시면 크게 보실 수 있습니다> |

업계는 차세대 트랜지스터 구조인 GAA(게이트 올 어라운드) 방식을 적용한 공정의 안정적인 수율 확보가 2㎚ 양산 성패를 좌우할 것으로 보고 있다. 회로가 점점 더 미세하게 좁아질수록 2011년부터 업계에서 사용해온 기존 핀펫(FinFET) 방식을 적용하는 데 한계가 있기 때문이다. 핀펫 공정은 상어 지느러미(Fin)처럼 생긴 차단기로 전류를 막아 초미세 선폭에서 누설되는 전류량이 많지만, GAA는 전류가 흐르는 채널을 4면으로 둘러싸 전류의 흐름을 더욱 세밀하게 조정할 수 있다.

삼성전자는 세계 최초로 3㎚ 공정에 GAA 기술을 적용한 만큼 업계 1위 TSMC보다 높은 기술 수준을 보일 수 있다고 자신한다. 삼성전자에 따르면 이 공정은 기존 5㎚ 핀펫 공정보다 전력은 45% 절감되고 성능은 23% 향상된다.

TSMC는 3㎚ 공정까지 기존 핀펫 구조를 유지하고, 2㎚ 이하 공정부터 GAA를 도입한다는 계획이다. 그 사이 삼성전자는 3㎚ 공정에 GAA 방식을 개선한 MBCFET(멀티브릿지패널FET) 구조를 적용하는 등 초미세공정에서 경쟁력을 쌓고 있다. MBCFET은 종이처럼 얇고 긴 모양의 나노 시트(Nano Sheet)를 쌓아 트랜지스터 성능과 전력 효율을 한 단계 더 높이는 삼성 고유 기술이다.

삼성전자는 이런 기술 경쟁력을 최우선 가치로 두고 시장 지배력을 강화한다는 전략이다. 최시영 삼성전자 파운드리사업부 사장은 지난 27일 한국공학한림원 포럼에서 “지난해 개발해 양산 중인 3㎚ MBCFET로 기술 리더십을 다시 가져올 것”이라며 “캐파(생산량) 측면에서도 괄목할 정도로 역량을 키워 고객에 맞는 사업을 펼쳐갈 계획”이라고 말했다.

최지희 기자(hee@chosunbiz.com)

<저작권자 ⓒ ChosunBiz.com, 무단전재 및 재배포 금지>

이 기사의 카테고리는 언론사의 분류를 따릅니다.

기사가 속한 카테고리는 언론사가 분류합니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.