|

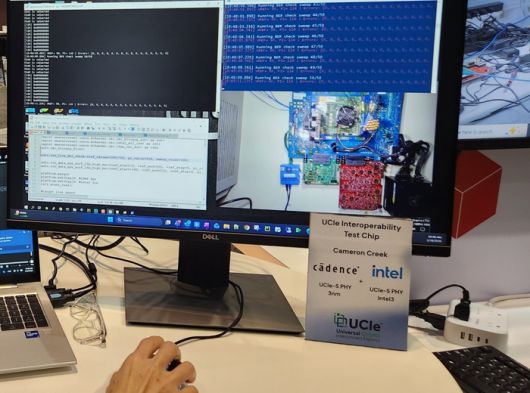

인텔과 케이던스가 제조한 UCIe-S 테스트칩(사진=마얀크 바트나가르 케이던스 제품 마케팅 이사 블로그) |

<이미지를 클릭하시면 크게 보실 수 있습니다> |

인텔과 반도체 설계자동화(EDA) 기업 케이던스가 서로 다른 반도체 설계자산(IP)를 결합해 작동하는 테스트 반도체 칩 개발에 성공했다. 반도체 성능 고도화 방법론으로 주목받는 이종 결합 표준 '칩렛'을 이용한 방식이다.

5일 업계에 따르면, 지난달 미국에서 개최된 칩렛 서밋 2026에서 인텔과 케이던스는 공동으로 개발한 UCIe-S 테스트 칩을 업계 처음으로 공개했다.

UCIe는 기업마다 서로 다른 반도체 연결 규격을 표준화한 것이다. 2022년 UCIe 컨소시엄이 발족돼 표준화를 주도하고 있다. 삼성전자·TSMC·인텔·퀄컴·MS·구글 등 글로벌 반도체 기업과 빅테크가 참여하고 있다.

UCIe-S는 표준 규격 중 하나로 보다 보편적인 칩 패키지에 적용할 수 있다. 범용성이 높다는 의미다.

인텔과 케이던스는 이번 테스트 칩을 통해 각기 보유한 설계자산(IP)를 결합, 상호 운용에 문제가 없다는 것을 입증했다. 인텔은 시스템온칩(SoC)과 메모리를 연결하는 인터페이스 IP인 '파이(PHY)'를, 케이던스는 UCIe 컨트롤러와 IP를 통합했다.

이를 통해 16G 수준의 고속 데이터 통신이 가능하다고 케이던스 측은 강조했다. 테스트칩은 3나노미터(㎚) 공정에서 제조됐다.

이번 사례는 서로 다른 반도체뿐만 아니라 제조사가 다른 설계까지 안정적으로 통합해 주목된다. 지금까지 UCIe 칩렛 상용화 사례는 몇 차례 있었지만, 주로 단일 제조사에서 이뤄졌다. 인텔과 케이던스의 각기 다른 기능을 하는 반도체 IP가 결합·운용돼, 칩렛 적용 범위를 넓힐 계기가 될 것으로 분석된다.

케이던스 관계자는 “이번 테스트 칩 시연은 인텔과 케이던스가 표준과 엄격한 엔지니어링 노력이 결합될 때 진정한 생태계 발전을 이끌어낼 수 있다는 것을 보여준 사례”라고 말했다.

권동준 기자 djkwon@etnews.com

[Copyright © 전자신문. 무단전재-재배포금지]

이 기사의 카테고리는 언론사의 분류를 따릅니다.

기사가 속한 카테고리는 언론사가 분류합니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.