기계硏·한화정밀기계·크레셈·엠티아이 공동 개발…정밀도 30% 이상 개선

|

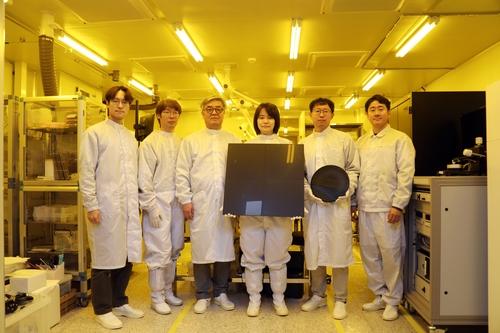

반도체 대면적 패키징 기술 개발한 연구팀 |

(대전=연합뉴스) 박주영 기자 = 한국기계연구원(기계연)은 송준엽 연구위원·이재학 박사 연구팀과 한화정밀기계, 크레셈, 엠티아이 연구팀이 공동으로 가로 600㎜, 세로 600㎜의 대면적 패널에 반도체 칩을 패키징할 수 있는 차세대 'FO-PLP 기술'을 개발했다고 26일 밝혔다.

반도체 패키징은 회로가 새겨진 반도체 칩에 전기적 연결을 해주고 외부 충격으로부터 안전하게 보호하는 밀봉 공정이다.

FO-PLP는 반도체 칩을 웨이퍼(기판)에 하나씩 조립하는 기존 FO-WLP 방식과 달리 패널 단위로 한꺼번에 패키징할 수 있어 생산성이 높다.

다만 칩을 대면적 패널 위에 배열하는 과정에서 오차가 생기거나 재료 간 열팽창 계수(온도 상승에 따른 부피 변화 값) 차이로 인해 칩 틀어짐 현상이 발생할 수 있다.

연구팀은 공정 통합형 AI 검사와 보정 기술을 통해 칩 틀어짐 오차를 ±5㎛(마이크로미터·100만분의 1m) 수준으로 줄여 높은 정밀도를 달성했다. 기존보다 30% 이상 개선된 수준이다.

|

연구팀이 개발한 반도체 패키징 용 대면적 패널 |

또 시간당 1만개 이상의 칩을 생산할 수 있어 기존 300㎜ 원형 페이퍼를 이용한 FO-WLP 장비에 비해 생산성을 6.5배 이상 높일 수 있다.

송준엽 연구위원은 "FO-PLP 시장은 앞으로 5년간 연평균 성장률이 30%로 예측되는 고성장 분야"라며 "반도체 수율과 생산성을 높이는 데 기여할 것"이라고 말했다.

기계연은 이날 서울 엘타워 루비홀에서 한국반도체연구조합, 한화정밀기계, 크레셈, 엠티아이와 차세대 반도체 FO-PLP 기술 상용화를 위한 업무협약을 체결했다.

jyoung@yna.co.kr

▶제보는 카카오톡 okjebo

▶연합뉴스 앱 지금 바로 다운받기~

▶네이버 연합뉴스 채널 구독하기

<저작권자(c) 연합뉴스, 무단 전재-재배포, AI 학습 및 활용 금지>

이 기사의 카테고리는 언론사의 분류를 따릅니다.

기사가 속한 카테고리는 언론사가 분류합니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.