JEDEC "차세대 표준 완성 단계"

SK하이닉스, 대만 TSMC와 동맹

삼성전자, '턴키 전략' 강화

22일 국제반도체표준협의기구(JEDEC) 솔리드스테이트 기술 협회는 최근 "HBM4 표준이 완성에 가까워지고 있다"고 밝혔다. JEDEC이 HBM4 표준 제정 진행 상황에 관해 발표한 것은 처음이다.

JEDEC은 글로벌 반도체·테크 기업이 모인 단체다. 반도체 업체와 고객사 등의 의견을 구해 D램·낸드플래시 등 메모리 반도체는 물론 인터페이스·패키징 등 반도체 공급망 전반의 표준 규격을 만든다. JEDEC 표준은 신형 반도체 설계·제작을 위한 지침서라고 볼 수 있겠다. 표준 완성을 기점으로 본격적인 HBM4 개발이 가능해지는 셈이다.

|

<이미지를 클릭하시면 크게 보실 수 있습니다> |

JEDEC은 완성 단계에 접어든 HBM4의 규격 일부를 공개했다. 성능 기준점은 기존에 알려진 것과 유사한 수준이다. HBM4는 12단에 머물던 HBM3·HBM3E보다 한 차원 높은 최대 16단을 지원한다. 이는 단위면적 당 용량이 커지고 속도도 더욱 빨라짐을 의미한다. D램당 용량도 기존 최대 24Gb(기가비트)에서 32Gb로 확장된다. 층수가 높아질 뿐 아니라 층 당 용량 밀도도 높아지는 셈이다.

또 기존 1028비트(bit)인 층 당 채널 수가 2048비트로 두 배 늘어나고 반도체 칩 면적이 더 크다는 점도 확인했다. 채널 당 속도는 6.4Gbps(초당 기가비트)로 초기 합의가 마무리됐다. 이 속도는 더 높아질 가능성이 크다. 이미 시장에 공급 중인 HBM3E가 8Gbps를 지원하고 있기 때문이다.

다만, JEDEC은 적층 높이에 대해서는 언급하지 않았다. 당초 JEDEC은 올 초 HBM4 규격을 공개할 예정이었으나 적층 높이에 대한 회원사 간 이견으로 발표가 늦어졌다고 한다. JEDEC은 기존 720마이크로미터(μm)에서 775μm로 높이 제한을 완화하려는 것으로 알려져 있다. 더 높은 단 수를 쌓기 위해서는 여유 공간이 필요한 탓이다.

|

<이미지를 클릭하시면 크게 보실 수 있습니다> |

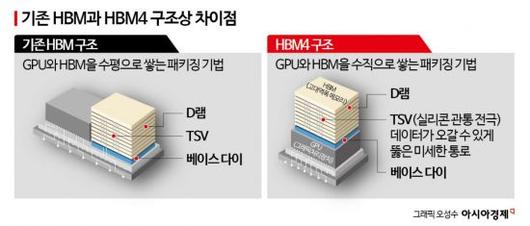

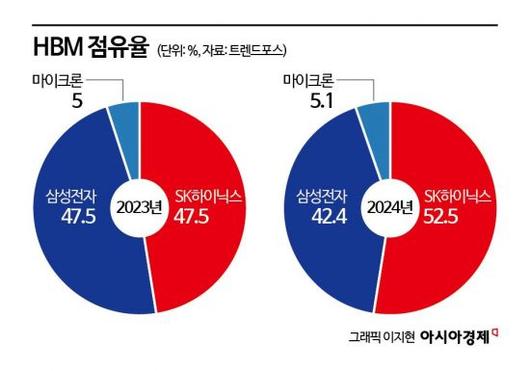

제품 규격이 두곽을 드러내는 만큼, 메모리 업계는 HBM4 양산 준비에 더욱 만전을 기하고 있다. HBM을 둘러싼 진짜 승부처는 HBM4가 될 것이기 때문이다. 6세대 HBM4는 설계부터 제조까지 기존 제품과는 차원이 다른 난도가 요구된다.

AI 반도체 핵심 고객사인 엔비디아는 지난 6월 컴퓨텍스 기조연설에서 2026년 출시되는 '루빈' 플랫폼에 HBM4 8개를 처음으로 탑재하고, 2027년 '루빈 울트라'에는 HBM4 12개를 탑재한다고 로드맵을 통해 밝혔다. AMD 또한 2026년 출시하는 'MI400'에 처음으로 HBM4를 탑재한다는 계획이다.

HBM 리더십을 지켜왔던 SK하이닉스는 차세대 HBM 생산과 어드밴스드 패키징 기술 역량을 강화하기 위해 대만 TSMC와 긴밀히 협력하기로 했다. 양사는 최근 대만 타이페이에서 기술 협력을 위한 양해각서(MOU)를 체결, HBM4를 개발한다는 계획이다.

각 분야에서 강점을 가진 업체들끼리 협력하기로 한 만큼 자신감을 내비치고 있다. SK하이닉스는 최근 HBM4의 양산 시기를 1년가량 앞당겨 2025년에 양산하겠다고 밝힌 바 있다. 주요 빅테크 기업들의 요구사항을 충족시키고 빠르게 고객을 확보하려는 전략으로 풀이된다.

양사는 우선 HBM 패키지 내 최하단에 탑재되는 베이스 다이(Base Die)의 성능 개선에 나선다. HBM은 베이스 다이 위에 D램 단품 칩인 코어 다이(Core Die)를 쌓아 올린 뒤 이를 TSV 기술로 수직 연결해 만들어진다. 베이스 다이는 GPU와 연결돼 HBM을 컨트롤하는 역할을 수행한다.

SK하이닉스는 5세대인 HBM3E까지는 자체 공정으로 베이스 다이를 만들었으나, HBM4부터는 로직(Logic) 선단 공정을 활용할 계획이다. 이 다이를 생산하는 데 초미세 공정을 적용하면 다양한 기능을 추가할 수 있기 때문이다. 회사는 이를 통해 성능과 전력 효율 등 고객들의 폭넓은 요구에 부합하는 맞춤형 HBM을 생산한다는 계획이다. 이와 함께, SK하이닉스는 HBM과 TSMC가 특허권을 갖고 있는 고유 공정 CoWoS 기술 결합해 고객 요청에도 공동 대응하기로 했다.

|

<이미지를 클릭하시면 크게 보실 수 있습니다> |

삼성전자는 HBM4를 HBM 역전의 기회로 삼겠다는 복안이다. 삼성전자는 시스템LSI사업부와 파운드리사업부를 모두 보유하고 있어, HBM4 베이스 다이 초기 설계부터 성능 최적화를 위해 함께 움직일 수 있기 때문이다. 엔비디아 같은 칩 제조사는 파운드리와 패키징 등 전체 프로세스를 단일 업체에 맡기고 싶어 하기 때문에 삼성전자가 강점으로 내세우는 이른바 '턴키(일괄생산)' 전략으로 수주전에서 경쟁력을 보일 수 있다.

특히, 삼성전자가 HBM에 적용 중인 비전도성필름(NCF) 기술은 고적층에 유리해 단수가 16층으로 높아지는 HBM4에 최적이라는 평가를 받고 있다. 삼성전자는 더 낮은 높이로도 고적층이 가능한 하이브리드본딩 기술 개발에도 속도를 내고 있다. 지난 4월에는 하이브리드본딩을 적용해 16단 HBM4를 구현했다고 밝히기도 했다.

삼성전자는 최근 '삼성 파운드리 포럼'을 통해 HBM4부터 고객 맞춤형 제품을 현실화하겠다는 입장을 밝히기도 했다. 삼성전자는 고객사에게 HBM D램과 파운드리, 첨단 패키징 등을 일괄 제공하는 'AI 솔루션' 전략을 제시한 바 있다.

한예주 기자 dpwngks@asiae.co.kr

<ⓒ투자가를 위한 경제콘텐츠 플랫폼, 아시아경제(www.asiae.co.kr) 무단전재 배포금지>

이 기사의 카테고리는 언론사의 분류를 따릅니다.

기사가 속한 카테고리는 언론사가 분류합니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.