[디지털투데이 양대규 기자] 반도체 업계에서는 실리콘 기반의 반도체가 더 이상 '무어의 법칙'에 따라 성능이 증가하지 않을 것이라는 우려가 나오고 있다. 실리콘 트랜지스터의 성장이 멈추고 점점 비효율적이 될 때가 다가온다는 것이다. 하지만 최근 MIT에서 기존의 실리콘이 아닌 탄소 나노튜브(CNT) 기반의 새로운 반도체를 개발하며, 반도체 업계에 새로운 바람을 불러일으키고 있다.

23일 반도체 업계에 따르면, 최근 MIT의 연구원들이 산업 표준 설계 흐름과 공정을 이용해 탄소 나노튜브 트랜지스터를 사용한 16비트 RISC-V 마이크로프로세서(MPU)를 만드는 데 성공했다. 이는 실리콘 마이크로프로세서보다 10배 높은 에너지 효율을 보이는 것으로 나타났다.

연구에 참여한 EECS(전자 엔지니어링&컴퓨팅 과학) 슈레이커 교수는 "실리콘에는 한계가 있다"며, "우리가 계속해서 컴퓨팅에서 우위를 차지하기를 원한다면 탄소 나노튜브는 그 한계를 극복하는 가장 유망한 방법 중 하나다. 이 논문은 탄소 나노튜브로 칩을 만드는 방법을 완전히 재조명한다"고 설명했다.

최근 실리콘 반도체의 성장이 한계에 다다르며, 업계에서는 실리콘을 능가하는 새로운 소자 기술에 대해 연구를 진행하고 있는 상황이다.

전문가들은 새로운 소자 기술인 탄소 나노튜브 전계효과 트랜지스터(CNFET) 기반 디지털 회로가 상당한 에너지 효율 편익을 보장하는 하나의 접근방식을 제공하지만, 나노스케일의 결함과 탄소 나노튜브의 가변성 제어가 어려워, 큰 규모의 통합 시스템의 실현은 어려웠다고 설명한다.

하지만 최근 MIT 연구원들은 네이처(Nature)에 CNFET로 제작된 실리콘 이상의 성능을 보이는 새로운 MPU에 대해 70페이지 분량의 논문을 게재했다. 해당연구는 미국 국방고등연구계획국(DARPA), 아나로그디바이스, 국립과학재단, 공군연구소 등의 지원을 받았다.

|

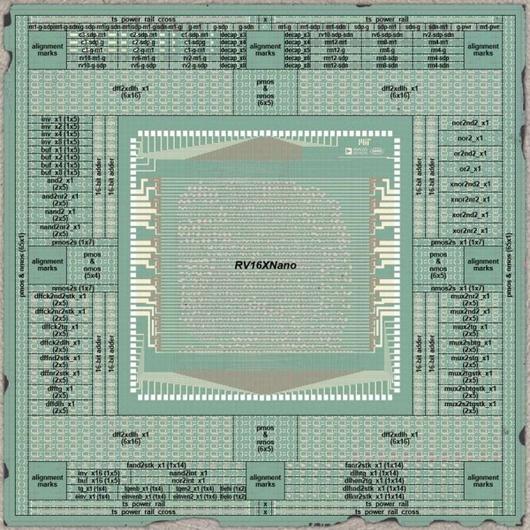

연구진이 개발한 RV16X-NANO 다이의 현미경 이미지(사진=네이처) |

<이미지를 클릭하시면 크게 보실 수 있습니다> |

RISC-V 아키텍처 기반 탄소 나노튜브 반도체

발표된 16비트 MPU는 RISC-V 아키텍처를 기반으로 만들어졌다. RISC-V 아키텍처는 ARM의 모바일 아키텍처에 대응하는 새로운 오픈 소스 기술로 주목받고 있다. 제품은 16비트 데이터와 주소에 대해 표준 32비트 명령을 실행한다. 1만 4000개 이상의 보완 메탈-옥사이드-반도체 CNFET로 구성되며 산업 표준 설계 흐름과 프로세스를 사용해 설계·제작된다.

연구에 따르면 CNFET는 실리콘에 비해 에너지 효율이 약 10배, 속도가 훨씬 빠른 특성을 가지고 있다. 그러나 스케일로 가공할 때 트랜지스터는 성능에 영향을 미치는 결함이 많이 발생하기 때문에 실용성이 떨어지는 상황이다.

EE타임즈는 "MIT 연구원들이 개발한 기술은 전통적인 실리콘 칩 주조 공장의 공정을 이용해, CNFET를 제작할 때 결함을 극적으로 제한하고 완전한 기능 제어를 가능하게 한다"며, "RISC-V 오픈 소스 칩 아키텍처에 기반한 그들의 CNFET 기반 마이크로프로세서는 전체 명령을 정확하게 실행할 수 있었다"고 보도했다.

논문의 공동 저자인 맥스 M은 "이 칩은 고성능과 에너지 효율이 높은 컴퓨팅을 약속하는 나노 기술로 만들어진 가장 진보된 칩"이라고 강조했다.

|

기존의 실리콘 웨이퍼(사진=램리서치) |

CNT 요구조건 8나인→4나인으로 1만배 낮춰

이상적으로 CNFET는 비트 1과 0에 해당하는 전도성을 OFF로 전환하기 위해 특성이 필요하다. 하지만 탄소 나노튜브의 작은 영역이 금속성이 되면서 트랜지스터의 전환을 늦추거나 멈추게 하는 문제가 지속적으로 제기됐다.

전문가들은 이런 고장을 버티려면, 약 99.999999%(8나인)의 순도의 탄소 나노튜브를 필요로 한다고 지적한다. 이런 고순도 탄소 나노튜브의 양산은 사실상 불가능한 수준이다.

이에 연구원들은 'DREAM'(금속화된 탄소 나노튜브의 복원력 디자인)이라는 기술을 고안했다. 이 기술은 금속 CNFET를 컴퓨팅에 지장을 주지 않도록 배치한다. 그렇게 함으로써, 연구진은 순도 요구조건을 크게 완화했다. 기존보다 1만 배 낮은 약 99.99%(4나인) 순도의 탄소 나노튜브로도 반도체 설계가 가능하다는 것이다.

슈레이커는 "DREAM의 말장난은 매우 의도적인 것이다. 왜냐하면 그것은 꿈의 해결책이기 때문"이라며, "이것을 통해 우리는 선반에 탄소 나노튜브를 웨이퍼에 떨어뜨리고, 다른 특별한 일도 하지 않고 그냥 정상처럼 회로를 만들 수 있다"고 설명했다.

연구진의 주요 목표는 칩을 양산하는 것이다. 이를 위해 연구진은 연구를 지원하는 DARPA의 프로그램을 통해 실리콘 칩 파운드리 제조 기법을 구현하고 있다. 탄소 나노튜브로 만들어진 칩의 공급 시점이 언제가 될지는 미정이지만, 슈레이커는 "5년 미만일 수 있다고" 말했다.

<저작권자 Copyright ⓒ 디지털투데이 (DigitalToday) 무단전재 및 재배포 금지>

이 기사의 카테고리는 언론사의 분류를 따릅니다.

언론사는 한 기사를 두 개 이상의 카테고리로 분류할 수 있습니다.